企業(yè)博客

更多>>解密振蕩器輸出邏輯,分析其應(yīng)用技巧

來源:http://diginow.com.cn 作者:康比電子 2020年09月19

解密振蕩器輸出邏輯,分析其應(yīng)用技巧

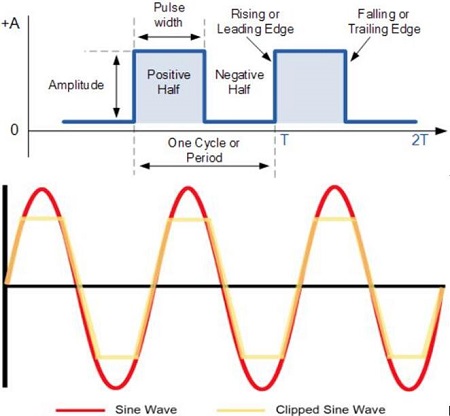

石英晶振的輸出邏輯分多鐘,且每一種的性能及特性都不盡相同,且輸出邏輯是有源晶振獨(dú)有特性,這是眾所周知的;但是常常在應(yīng)用過程中沒有重點(diǎn)去關(guān)注過這個(gè)問題,實(shí)際上它對(duì)產(chǎn)品的性能也存在極大的影響,甚至是影響設(shè)備的性能等等;那么在應(yīng)用過程中有沒有技巧呢?或者說有沒有什么樣的標(biāo)準(zhǔn)可以參考呢? 輸出類型總體可分為兩大類,分別是方波輸出和正玄波輸出,想要應(yīng)用我們就得對(duì)其足夠熟悉,否則一切都只不過是紙上談兵罷了;但是呢由于篇幅的原因,接下來就選取其中幾種常用的輸出類型進(jìn)行具體說明,如您想要了解更多的話可以聯(lián)系咨詢我們.

CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時(shí)鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能更適合您的特定需求.

PECL輸出經(jīng)常在高速時(shí)鐘分配電路中使用.這是因?yàn)镻ECL具有很高的抗噪能力,能夠在較長(zhǎng)的線路長(zhǎng)度上驅(qū)動(dòng)高數(shù)據(jù)速率,并且由于電壓擺幅較大而具有良好的抖動(dòng)性能.但是,PECL需要高功耗才能運(yùn)行,這是主要缺點(diǎn).LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但是提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會(huì)帶來挑戰(zhàn),因?yàn)樾枰私觼戆l(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查是否正確端接以達(dá)到最佳性能.

LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.對(duì)于更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,它們將需要更多的功耗.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

大體的話目前市場(chǎng)上較為常用的輸出方式就這幾種,除這幾種之外還有就是正玄波和削頂正弦波;其中CMOS,HCMOS和LVCMOS稱為方波輸出,通常會(huì)出現(xiàn)普通有源晶振,壓控晶振,壓控溫補(bǔ)晶振等產(chǎn)品上,而PECL以及LVDS雖也是方波形式的,但是這是一種差分輸出型號(hào),在以前是差分晶振獨(dú)有的輸出邏輯,不過如今已經(jīng)實(shí)現(xiàn)在普通有源晶振上搭載這樣的輸出邏輯了,NDK前段時(shí)間就推出過一款.

通過以上分析我們可得出一下結(jié)論:

1)因?yàn)長(zhǎng)VDS輸出在接收器處只需要一個(gè)電阻,而LVPECL在發(fā)送器和接收器上都需要端接.如果要便于使用的話可以選用LVDS輸出

2)LVDS,LVPECL和HCSL具有比CMOS更快的轉(zhuǎn)換速度,但需要更多的功率.這是針對(duì)于那種高頻輸出的產(chǎn)品

3)如果想要達(dá)到低功耗的目的,并且頻率高于150MHz的話,那么建議選用CMOS或者LVDS.

.jpg) 是的,以上三條準(zhǔn)則就是這些石英晶振輸出邏輯的應(yīng)用技巧,基本已經(jīng)囊括了所有的常用輸出類型,在應(yīng)用時(shí)廣大用戶可按需選擇.

是的,以上三條準(zhǔn)則就是這些石英晶振輸出邏輯的應(yīng)用技巧,基本已經(jīng)囊括了所有的常用輸出類型,在應(yīng)用時(shí)廣大用戶可按需選擇.

石英晶振的輸出邏輯分多鐘,且每一種的性能及特性都不盡相同,且輸出邏輯是有源晶振獨(dú)有特性,這是眾所周知的;但是常常在應(yīng)用過程中沒有重點(diǎn)去關(guān)注過這個(gè)問題,實(shí)際上它對(duì)產(chǎn)品的性能也存在極大的影響,甚至是影響設(shè)備的性能等等;那么在應(yīng)用過程中有沒有技巧呢?或者說有沒有什么樣的標(biāo)準(zhǔn)可以參考呢? 輸出類型總體可分為兩大類,分別是方波輸出和正玄波輸出,想要應(yīng)用我們就得對(duì)其足夠熟悉,否則一切都只不過是紙上談兵罷了;但是呢由于篇幅的原因,接下來就選取其中幾種常用的輸出類型進(jìn)行具體說明,如您想要了解更多的話可以聯(lián)系咨詢我們.

CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時(shí)鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能更適合您的特定需求.

PECL輸出經(jīng)常在高速時(shí)鐘分配電路中使用.這是因?yàn)镻ECL具有很高的抗噪能力,能夠在較長(zhǎng)的線路長(zhǎng)度上驅(qū)動(dòng)高數(shù)據(jù)速率,并且由于電壓擺幅較大而具有良好的抖動(dòng)性能.但是,PECL需要高功耗才能運(yùn)行,這是主要缺點(diǎn).LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但是提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會(huì)帶來挑戰(zhàn),因?yàn)樾枰私觼戆l(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查是否正確端接以達(dá)到最佳性能.

LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.對(duì)于更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,它們將需要更多的功耗.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

大體的話目前市場(chǎng)上較為常用的輸出方式就這幾種,除這幾種之外還有就是正玄波和削頂正弦波;其中CMOS,HCMOS和LVCMOS稱為方波輸出,通常會(huì)出現(xiàn)普通有源晶振,壓控晶振,壓控溫補(bǔ)晶振等產(chǎn)品上,而PECL以及LVDS雖也是方波形式的,但是這是一種差分輸出型號(hào),在以前是差分晶振獨(dú)有的輸出邏輯,不過如今已經(jīng)實(shí)現(xiàn)在普通有源晶振上搭載這樣的輸出邏輯了,NDK前段時(shí)間就推出過一款.

通過以上分析我們可得出一下結(jié)論:

1)因?yàn)長(zhǎng)VDS輸出在接收器處只需要一個(gè)電阻,而LVPECL在發(fā)送器和接收器上都需要端接.如果要便于使用的話可以選用LVDS輸出

2)LVDS,LVPECL和HCSL具有比CMOS更快的轉(zhuǎn)換速度,但需要更多的功率.這是針對(duì)于那種高頻輸出的產(chǎn)品

3)如果想要達(dá)到低功耗的目的,并且頻率高于150MHz的話,那么建議選用CMOS或者LVDS.

.jpg)

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2024-02-18]Greenray晶體振蕩器專為國防和航...

- [2024-01-20]HELE加高產(chǎn)品和技術(shù)及熱門應(yīng)用

- [2024-01-20]HELE加高一個(gè)至關(guān)重要的組件晶體...

- [2023-12-28]Suntsu晶振最新的射頻濾波器突破...

- [2023-12-28]Qantek提供各種高可靠性微處理器...

- [2023-10-11]日本納卡石英晶體的低老化領(lǐng)先同...

- [2023-09-25]遙遙領(lǐng)先H.ELE開啟汽車創(chuàng)新

- [2023-09-23]瑞薩電子MCU和MPU產(chǎn)品領(lǐng)先同行