企業(yè)博客

更多>>常用Oscillator輸出方式之間的性能差異如何?

來(lái)源:http://diginow.com.cn 作者:康比電子 2020年12月22

常用Oscillator輸出方式之間的性能差異如何?

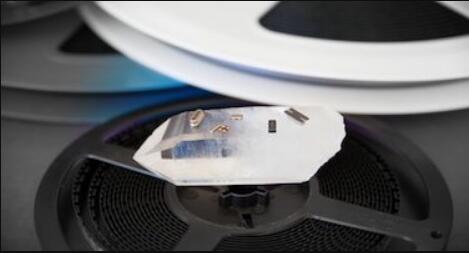

Oscillator相比較于無(wú)源石英晶振來(lái)說(shuō)有本質(zhì)性的區(qū)別,具備輸出方式就是其中之一;輸出方式即是頻率型號(hào)的輸出形式,通常有方波和正玄波兩種,并且采用不同輸出方式的石英晶振產(chǎn)品的性能也是有區(qū)別的,那么他們之間的差異究竟如何呢?

我們常用的輸出邏輯有CMOS,HCMOS,LVCMOS以及差分輸出里面的LVDS輸出和正玄波、削頂正玄波,CMOS,HCMOS,LVCMOS這幾種輸出方式是單端輸出里的,信號(hào)波形呈現(xiàn)方波形狀,所以又稱之為方波;而LVDS這種輸出方式是以往是在差分晶振上應(yīng)用的,不過(guò)隨著技術(shù)的發(fā)展,如今在SPXO晶振也能夠輸出這樣的差分型號(hào);下面我們就這幾個(gè)常用輸出方式進(jìn)行對(duì)比講解. CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時(shí)鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來(lái)有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能更適合您的特定需求.這三種輸出邏輯雖然驅(qū)動(dòng)功率比較大,但是有一個(gè)致命的缺點(diǎn)那就是諧波分量較多,產(chǎn)生的相位噪聲比較大,對(duì)晶振頻率信號(hào)穩(wěn)定的影響也非常大.

LVDS又稱為低壓差分信號(hào),LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.差分晶振通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.為了獲得更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,其功耗更高.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

差分輸出提供相位相差180°的雙路輸出信號(hào)線,這對(duì)信號(hào)有諸多好處,比如可以更好的上調(diào)和下調(diào)時(shí)間,再比如具備出色的抖動(dòng)和相位噪聲性能,并且擁有改進(jìn)過(guò)后的共模噪聲抑制,還能夠幫助減少電磁和射頻干擾.

最后就是正玄波和削頂正玄波輸出邏輯了,這種方式是信號(hào)輸出的理想狀態(tài),所以它自身所產(chǎn)生的諧波分量非常小,不似差分信號(hào)那般是通過(guò)兩個(gè)信號(hào)正交消除諧波分量那般;但是它有一個(gè)致命的缺點(diǎn)就是驅(qū)動(dòng)功率非常小.

正弦波-是晶體或振蕩器電路的標(biāo)準(zhǔn)或”自然”信號(hào)輸出.它由一個(gè)基本正弦頻率輸出組成.線性正弦波輸出在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號(hào)的應(yīng)用.削波正弦波-正弦波輸出受到控制,因此不會(huì)達(dá)到其最大高電平或低電平.這樣,您將創(chuàng)建一個(gè)方波輸出,而不會(huì)犧牲任何所需的相位噪聲性能.

這樣的話,各種輸出方式之間的性能之間的差異就一目了然了吧;所以在設(shè)計(jì)或者應(yīng)用過(guò)程中選用的時(shí)候需要格外注意,因?yàn)樗鼤?huì)影響到有源晶振產(chǎn)品的精度,功耗,相位噪聲,地抖動(dòng)等性能.

常用Oscillator輸出方式之間的性能差異如何?

Oscillator相比較于無(wú)源石英晶振來(lái)說(shuō)有本質(zhì)性的區(qū)別,具備輸出方式就是其中之一;輸出方式即是頻率型號(hào)的輸出形式,通常有方波和正玄波兩種,并且采用不同輸出方式的石英晶振產(chǎn)品的性能也是有區(qū)別的,那么他們之間的差異究竟如何呢?

我們常用的輸出邏輯有CMOS,HCMOS,LVCMOS以及差分輸出里面的LVDS輸出和正玄波、削頂正玄波,CMOS,HCMOS,LVCMOS這幾種輸出方式是單端輸出里的,信號(hào)波形呈現(xiàn)方波形狀,所以又稱之為方波;而LVDS這種輸出方式是以往是在差分晶振上應(yīng)用的,不過(guò)隨著技術(shù)的發(fā)展,如今在SPXO晶振也能夠輸出這樣的差分型號(hào);下面我們就這幾個(gè)常用輸出方式進(jìn)行對(duì)比講解. CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時(shí)鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來(lái)有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能更適合您的特定需求.這三種輸出邏輯雖然驅(qū)動(dòng)功率比較大,但是有一個(gè)致命的缺點(diǎn)那就是諧波分量較多,產(chǎn)生的相位噪聲比較大,對(duì)晶振頻率信號(hào)穩(wěn)定的影響也非常大.

LVDS又稱為低壓差分信號(hào),LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.差分晶振通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.為了獲得更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,其功耗更高.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

差分輸出提供相位相差180°的雙路輸出信號(hào)線,這對(duì)信號(hào)有諸多好處,比如可以更好的上調(diào)和下調(diào)時(shí)間,再比如具備出色的抖動(dòng)和相位噪聲性能,并且擁有改進(jìn)過(guò)后的共模噪聲抑制,還能夠幫助減少電磁和射頻干擾.

最后就是正玄波和削頂正玄波輸出邏輯了,這種方式是信號(hào)輸出的理想狀態(tài),所以它自身所產(chǎn)生的諧波分量非常小,不似差分信號(hào)那般是通過(guò)兩個(gè)信號(hào)正交消除諧波分量那般;但是它有一個(gè)致命的缺點(diǎn)就是驅(qū)動(dòng)功率非常小.

正弦波-是晶體或振蕩器電路的標(biāo)準(zhǔn)或”自然”信號(hào)輸出.它由一個(gè)基本正弦頻率輸出組成.線性正弦波輸出在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號(hào)的應(yīng)用.削波正弦波-正弦波輸出受到控制,因此不會(huì)達(dá)到其最大高電平或低電平.這樣,您將創(chuàng)建一個(gè)方波輸出,而不會(huì)犧牲任何所需的相位噪聲性能.

這樣的話,各種輸出方式之間的性能之間的差異就一目了然了吧;所以在設(shè)計(jì)或者應(yīng)用過(guò)程中選用的時(shí)候需要格外注意,因?yàn)樗鼤?huì)影響到有源晶振產(chǎn)品的精度,功耗,相位噪聲,地抖動(dòng)等性能.

常用Oscillator輸出方式之間的性能差異如何?

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2023-09-04]Abracon晶振5G小型蜂窩的時(shí)序參...

- [2023-08-31]CTS運(yùn)輸產(chǎn)品手冊(cè)

- [2020-12-22]常用Oscillator輸出方式之間的性...

- [2019-07-25]負(fù)載電容決定晶振的共振頻率

- [2019-06-24]探討MEMS晶振第一和附加工藝的關(guān)...

- [2019-05-21]石英晶體諧振器縱向振動(dòng)

- [2019-04-27]有源晶振啟動(dòng)時(shí)間

- [2019-03-15]每個(gè)工程師應(yīng)該知道有源晶振